A recently developed breadboard version of an advanced signal processor for arraying many antennas in NASA's Deep Space Network (DSN) can accept inputs in a 500-MHz-wide frequency band from six antennas. The next breadboard version is expected to accept inputs from 16 antennas, and a following developed version is expected to be designed according to an architecture that will be scalable to accept inputs from as many as 400 antennas. These and similar signal processors could also be used for combining multiple wide-band signals in non-DSN applications, including very-long-baseline interferometry and telecommunications.

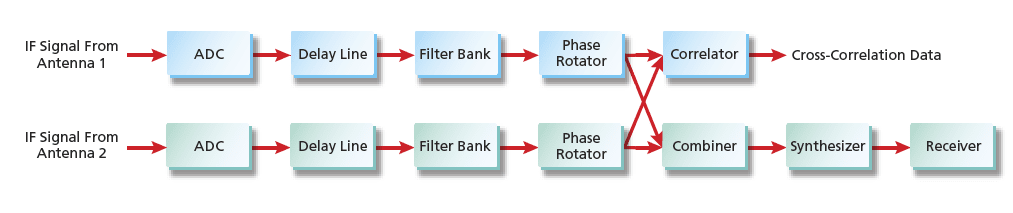

The inputs from the antennas are preprocessed signals in an intermediate- frequency (IF) band from 700 to 1,200 MHz. High-speed commercial offthe- shelf analog-to-digital-converter (ADC) integrated circuits sample the inputs to 8 bits at a rate of 1,280 MHz. The sample data are transmitted via fiber-optic links to signal-processing boards in a commercial high-performance, modular, digital chassis that conforms to an industry standard known as the Advanced Telecommunications Architecture (ATCA). The physical and electrical characteristics of an ATCA chassis are governed by a specification known as PICMG 3.0 (wherein "PICMG" signifies the PCI Industrial Computer Manufacturers Group and "PCI" signifies peripheral component interface).

Mounted on each signal-processing board are four field-programmable gate array (FPGA) integrated-circuit chips that are interconnected both on the board and through the ATCA back plane by serial links capable of operating at speeds up to 2.5 Gb/s. Each FPGA chip can be programmed, independently of the other FPGA chips, to perform such specific functions as implementing filter banks to convert time-domain data to frequencydomain data in frequency channels, wideand narrow-band cross-correlation, combining of the individual frequency channels, and implementing synthesizing filter banks for converting frequencydomain data back to the time domain.

This work was done by Andre Jongeling, Elliott Sigman, Kumar Chandra, Joseph Trinh, Melissa Soriano, Robert Navarro, Stephen Rogstad, Charles Goodhart, Robert Proctor, Michael Jourdan, and Benno Rayhrer of Caltech for NASA's Jet Propulsion Laboratory.

This Brief includes a Technical Support Package (TSP).

Breadboard Signal Processor for Arraying DSN Antennas

(reference NPO-43646) is currently available for download from the TSP library.

Don't have an account?

Overview

The document is a Technical Support Package from NASA's Jet Propulsion Laboratory (JPL) detailing the Breadboard Signal Processor for Arraying Deep Space Network (DSN) Antennas, identified as NPO-43646. It outlines the development and implementation of a signal processing breadboard designed to enhance the capabilities of the DSN by enabling the coherent arraying of a large number of antennas, specifically over a bandwidth of 500 MHz.

The breadboard system implements an architecture based on the concepts described in NASA Technical Report (NTR) 41145, utilizing Field Programmable Gate Arrays (FPGAs) to process antenna signals. The system accepts intermediate frequency (IF) signals within a 500 MHz bandwidth, sampling them at 1280 MHz using specific Atmel chips. The digitized signals are then transmitted to processing boards that fit within the PICMG 3.0 Advanced Telecommunications Computing Architecture (ATCA) framework. Each processing board is equipped with four Xilinx XC2VP50 chips, which can be programmed for various signal processing tasks, including converting time-domain data to frequency channels and performing cross-correlation.

The document highlights the novelty of this work, emphasizing its ability to array over 100 antennas while combining signal processing for a wideband FX correlator with beamforming capabilities. The system is designed to handle terabits of information efficiently, addressing the challenges posed by the need for high bandwidth and robust performance in the face of potential component failures.

The development of this breadboard signal processor is driven by the requirements of the DSN Large Array task, which necessitated new technologies to improve signal-to-noise ratios and facilitate system calibration. The architecture incorporates state-of-the-art commercial off-the-shelf components, including analog-to-digital converters and fiber optic connectors, to create a test bed capable of processing large volumes of data.

In summary, this document provides a comprehensive overview of the advancements in signal processing technology for the DSN, showcasing the innovative approaches taken to enhance the performance and reliability of deep space communication systems. It serves as a resource for understanding the technical developments that have broader implications for aerospace-related technologies.