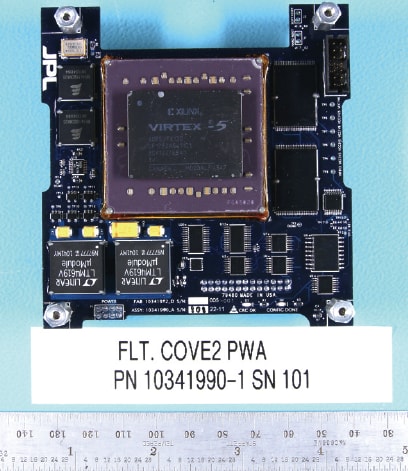

The COVE (CubeSat Onboard processing Validation Experiment) Payload Processor is JPL’s first on-orbit demonstration with the Xilinx Virtex-5 FPGA (field-programmable gate array). The electronics payload is designed to provide a platform for advanced data processing applications while conforming to CubeSat specifications. Measuring 9 × 9.5 × 2 cm, COVE carries the new radiation-hardened Virtex-5 FPGA (V5QV), magnetoresistive RAM (MRAM), and phase-change memory. All data access to/from the payload is facilitated through a shared memory interface via a direct serial peripheral interface (SPI). Multiple configuration options enable COVE to be reconfigured in flight with new FPGA firmware.

The COVE payload is designed with multiple power modes that enable the payload to save significant power when not actively processing data. Raw image data and processed results are written to and read back from COVE in a low power mode, where only the interfaces and shared memory are enabled and the FPGA remains off. Only during data processing is power provided to the FPGA.

The COVE payload processor has multiple ADCs to record housekeeping data. When the FPGA is on, all secondary board voltages, currents, and FPGA temperature are sampled by the ADCs and logged to shared memory. The MCubed flight computer downloads this data together with the image processing results prior to performing a transmission to ground stations.

The FPGA can be configured from multiple sources. A Xilinx XQF32P PROM is programmed on the ground and holds the “golden” configuration bitstream (FPGA firmware) for the experiment. This configuration cannot be overwritten in flight. A secondary FPGA configuration is stored in the shared memory and can be rewritten in flight. A discreet I/O line, controlled from the flight computer, tells the FPGA which configuration to boot on power-up. This dual-configuration design enables the COVE payload to be re-purposed for future experiments once the primary mission is completed.

M-Cubed was launched on October 28, 2011, from Vandenberg Air Force Base (VAFB) as a secondary payload of the NPP Mission. A post P-Pod deployment anomaly resulted in the inability to command M-Cubed, and therefore the COVE payload was not demonstrated on orbit. COVE-2 and a re-flight of M-Cubed was funded by NASA’s Earth Science Technology Office in May 2012 and was launched on December 5, 2013.

This work was done by Paula J. Pingree, Dmitriy L. Bekker, Brian R. Franklin, Andrew T. Klesh, Nooshin Meshkaty, Chris S. Peay, Thomas A. Werne, and Thor O. Wilson of Caltech; and Alireza Bakhshi of BA Engineering for NASA’s Jet Propulsion Laboratory. NPO-48112

This Brief includes a Technical Support Package (TSP).

COVE: A CubeSat Payload Processor

(reference NPO-48112) is currently available for download from the TSP library.

Don't have an account?

Overview

The document provides a comprehensive overview of the COVE (CubeSat On-board processing Validation Experiment), a project developed by NASA's Jet Propulsion Laboratory (JPL) at the California Institute of Technology. COVE aims to enhance the on-board processing capabilities of CubeSats, which are small, modular satellites used for various space missions.

The COVE project is centered around a reconfigurable FPGA (Field-Programmable Gate Array)-based processor designed to improve the computational efficiency and flexibility of CubeSat payloads. The document outlines the design, development, launch, and operational phases of the COVE project, emphasizing its significance in advancing CubeSat technology.

Key contributors to the project include Paula J. Pingree (Principal Investigator), Dmitriy Bekker, Matthew Bennett, Brian Franklin, Andy Klesh, Nooshin Meshkaty, Chris Peay, Thomas Werne, and Thor Wilson, all of whom are affiliated with JPL. The project has received sponsorship from NASA's Earth Science Technology Office (ESTO), highlighting its alignment with broader NASA objectives.

The document also references a press release from July 21, 2011, announcing the production of the Xilinx Space-Grade Virtex-5QV FPGA, which is integral to the COVE project due to its Mega-Rad capability, making it suitable for space applications. This technology is crucial for ensuring that CubeSats can perform complex tasks in the harsh environment of space.

Additionally, the document includes acknowledgments for the research conducted under NASA's sponsorship, emphasizing the collaborative nature of the project and its potential for wider technological, scientific, and commercial applications. It serves as a Technical Support Package (TSP) under NASA's Commercial Technology Program, aimed at disseminating aerospace-related developments.

Overall, the COVE project represents a significant step forward in CubeSat technology, providing a platform for testing advanced processing capabilities that could be applied to future space missions. The document serves as a valuable resource for understanding the project's objectives, methodologies, and potential impact on the field of aerospace engineering and satellite technology.