High-performance digital electronic circuits for onboard processing of return signals in an airborne precipitation - measuring radar system have been implemented in commercially available field - programmable gate arrays (FPGAs). Previously, it was standard practice to downlink the radar-return data to a ground station for postprocessing - a costly practice that prevents the nearly - real - time use of the data for automated targeting. In principle, the onboard processing could be performed by a system of about 20 personal - computer-type microprocessors; relative to such a system, the present FPGA-based processor is much smaller and consumes much less power. Alternatively, the onboard processing could be performed by an application-specific integrated circuit (ASIC), but in comparison with an ASIC implementation, the present FPGA implementation offers the advantages of (1) greater flexibility for research applications like the present one and (2) lower cost in the small production volumes typical of research applications.

The generation and processing of signals in the airborne precipitation- measuring radar system in question involves the following especially notable steps:

The generation and processing of signals in the airborne precipitation- measuring radar system in question involves the following especially notable steps:

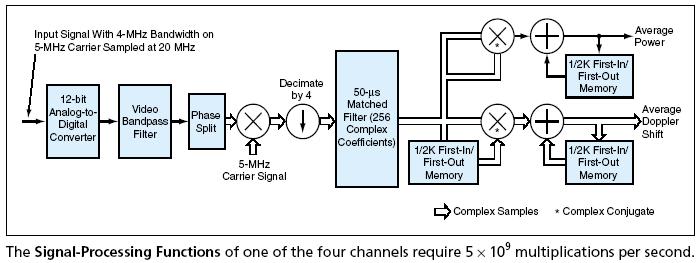

- The system utilizes a total of four channels - two carrier frequencies and two polarizations at each frequency.

- The system uses pulse compression: that is, the transmitted pulse is spread out in time and the received echo of the pulse is processed with a matched filter to despread it.

- The return signal is band-limited and digitally demodulated to a complex baseband signal that, for each pulse, comprises a large number of samples.

- Each complex pair of samples (denoted a range gate in radar terminology) is associated with a numerical index that corresponds to a specific time offset from the beginning of the radar pulse, so that each such pair represents the energy reflected from a specific range. This energy and the average echo power are computed.

- The phase of each range bin is compared to the previous echo by complex conjugate multiplication to obtain the mean Doppler shift (and hence the mean and variance of the velocity of precipitation) of the echo at that range.

The processing for each of the four channels (see figure) requires >5 × 109 multiplications per second - well beyond the capabilities of traditional microprocessors. The design effort involved the application of some algorithmic tricks, careful planning of the allocation of the areas on the FPGA to the various processing functions, and exploitation of the high circuit density and performance of the commercially available FPGAs chosen for this application. The design has made it possible to perform all the processing required by the radar system on two FPGAs - each one handling the data for two of the four channels. The algorithmic tricks and other design techniques used here could be applied to FPGA implementations of other signal-processing systems in other applications in radar, general imaging, and communications.

This work was done by Andrew Berkun and Ray Andraka of Caltech for NASA's Jet Propulsion Laboratory. For further information, access the Technical Support Package (TSP) free on-line at www.techbriefs.com/tsp under the Information Sciences category. NPO-30517

This Brief includes a Technical Support Package (TSP).

Digital Radar-Signal Processors Implemented in FPGAs

(reference NPO30517) is currently available for download from the TSP library.

Don't have an account?

Overview

The document is a Technical Support Package from NASA's Jet Propulsion Laboratory, focusing on Digital Radar-Signal Processors implemented in FPGAs (Field Programmable Gate Arrays). It outlines the advancements in radar technology, particularly in the context of meteorological applications, and emphasizes the benefits of using FPGAs for digital signal processing.

The document begins by discussing the significance of Doppler frequency output in radar systems, explaining how the phase and magnitude of the output relate to the movement of raindrops and the spread of velocities in echoes. This information is crucial for improving the accuracy of weather radar systems.

A key section of the document addresses pulse compression, a technique that enhances the signal-to-noise ratio of received echoes. It explains that while higher transmitted pulse power improves detection, it also presents challenges in transmitter design. To mitigate these issues, the document describes the use of long coded pulses, specifically linear frequency "chirps," which are compressed in the receiver using matched filters. This method allows for better range resolution without the need for excessively high peak power.

The document also highlights the advantages of bit serial arithmetic in FPGA designs. It contrasts bit serial and bit parallel designs, noting that bit serial structures process data one bit at a time, resulting in significant hardware reductions. This efficiency is particularly beneficial when the data rate is low, allowing for more effective use of FPGA capabilities.

Additionally, the document references various sources and studies that support the technical concepts discussed, including works on pulse compression radar and digital communication. It emphasizes the flexibility of digital processing, which allows for optimization of transmit waveforms and filtering techniques tailored to specific Doppler ranges.

Overall, the Technical Support Package serves as a comprehensive overview of the integration of digital radar signal processing with FPGA technology, showcasing its potential for enhancing radar systems in meteorology and other fields. It underscores NASA's commitment to advancing aerospace-related technologies with broader scientific and commercial applications, providing a foundation for future research and development in this area.