An interrupt is a signal in an interrupt controller (IC) that pulses to indicate an event or error. The IC is responsible for processing multiple internal interrupts and making these interrupts available to a host computer via a data bus or external output pins. Since there exist numerous interrupts, a method must be developed for routing the interrupts to the external output pins.

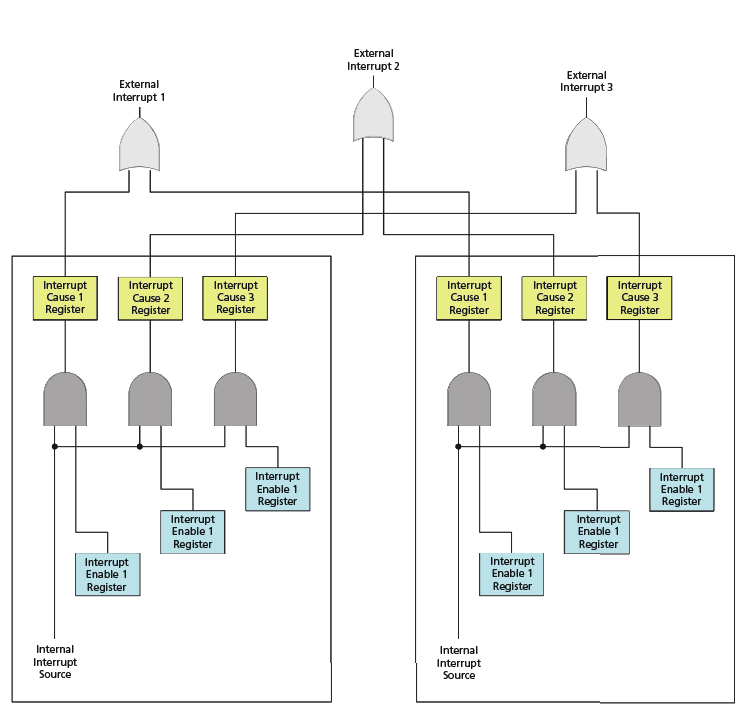

The fully configurable interrupt controller (see figure) provides one enable register per external interrupt desired. Each enable register is then logically combined (logical AND) with the internal interrupt to create one cause register per external interrupt. Then each external interrupt cause register is logically combined (logical OR) to create an external interrupt. This IC allows the host computer to select which internal interrupts to represent on any number of external pins by simply writing to the corresponding enable register.

This work was done by Nik D’Souza, Dean E. Sunderland, Terry J. Ahrendt, and Tim Moore of Honeywell for Johnson Space Center. For further information, contact the JSC Technology Transfer Office at (281) 483-3809. MSC-24768-1