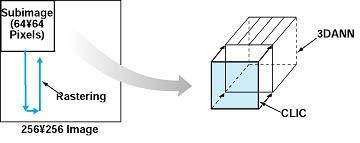

The column-loading input chip (CLIC) is a conceptual integrated-circuit chip that would serve as an interface between (1) any of various sources of image data and (2) a three-dimensional analog neural network (3DANN) of the type described in "Neural-Network Modules for High-Speed Image Processing" (NPO-19881), NASA Tech Briefs, Vol. 21, No. 10 (October 1997), page 26. The overall functions of the CLIC (see Figure 1) would be to load 8-bit digital image-intensity signals from a 64 × 64 array of pixels, convert these digital signals to an array of 64 × 64 analog voltages, and couple these voltages simultaneously to all of the corresponding 64 × 64 input terminals of the 3DANN. To prevent a data-input bottleneck, the CLIC is designed to perform these functions within a 3DANN-cycle time of 250 ns. The digital-to-analog conversion would be accomplished in only about 140 ns, leaving about 110 ns for processing by the 3DANN. The CLIC is also designed to satisfy requirements of compactness and low power consumption.

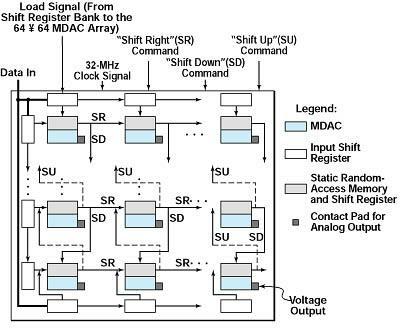

As part of the design to achieve the required high speed, the digital-to-analog-conversion would be performed locally for each of the 64 × 64 inputs to the 3DANN, by use of a 64 × 64 array of multiplying digital-to-analog converters (MDACs) at the corresponding locations. The input digital image-intensity signals for the MDACs would be coupled to the MDACs in pipeline fashion, by use of row and column arrays of 8-byte shift registers (see Figure 2).

The data would be shifted into the CLIC in parallel 8 bytes corresponding to rows or columns of pixels in the source image. It would be necessary to accommodate input in row or column groups of pixels in order to enable changes in direction of rastering when a 64 × 64 array of pixels reached the edge of a larger image of which it was a part.

For input in columns, the data would be shifted in rightward from the left edge; for input in rows, the data would be shifted in downward from the top edge or upward from the bottom edge. As the data for each successive column or row of new data was shifted in, the data already in each of the shift registers in the interior of the array would be shifted rightward (for input by columns) or up or down (for input by rows), and the data in the registers in the rightmost column (in the case of column input) or in the bottom or top row (in the case of row input) would be destroyed and replaced by new data.

While the data were being shifted into the CLIC, the MDACs would continue to operate on the data from the preceding 3DANN cycle. When all the data for a 64 × 64 array of pixels had been shifted in, all MDACs would simultaneously perform analog-to-digital conversions on the current contents of their local shift registers. After a settling time of about 140 ns, the analog output voltages of the MDACs would be ready for processing by the 3DANN. During the remaining 110 ns of the cycle, these voltages would continue to be available to the 3DANN for processing, and image data for the next cycle would be shifted in.

This work was done by Tuan A. Duong of Caltech for NASA's Jet Propulsion Laboratory.

In accordance with Public Law 96-517, the contractor has elected to retain title to this invention. Inquiries concerning rights for its commercial use should be addressed to

Technology Reporting Office

JPL

Mail Stop 122-116

4800 Oak Grove Drive

Pasadena, CA 91109

(818) 354-2240

Refer to NPO-20033

This Brief includes a Technical Support Package (TSP).

Column-loading input chip for neural-network module

(reference NPO20033) is currently available for download from the TSP library.

Don't have an account?

Overview

The document discusses advancements in spatial-temporal problem-solving through the development of a hardware-based solution known as the Three Dimensional Artificial Neural Network (3DANN). Traditional software approaches often struggle to provide timely solutions for complex problems, making hardware solutions essential. The 3DANN is designed to process information significantly faster than single-chip systems, achieving processing speeds of 250 nanoseconds by utilizing a 64-chip stack directly connected to a 64x64 infrared imager. This architecture allows for fully parallel data processing, eliminating delays associated with input image importation.

To enhance the versatility of the 3DANN, the document proposes an improved architecture that replaces the infrared imager with a new interface called the Column Loading Input Chip (CLIC). The CLIC serves as a bridge between various image data sources and the 3DANN, converting 8-bit digital image-intensity signals from a 64x64 pixel array into analog voltages. This conversion occurs within the 3DANN's cycle time of 250 nanoseconds, with the digital-to-analog conversion taking approximately 140 nanoseconds, leaving 110 nanoseconds for processing by the 3DANN. The design of the CLIC emphasizes compactness and low power consumption, addressing potential data-input bottlenecks and ensuring efficient operation.

The document also references the broader context of neural network modules for high-speed image processing, highlighting the significance of the CLIC in advancing these technologies. The CLIC's ability to couple analog voltages simultaneously to all input terminals of the 3DANN enhances the system's overall performance and adaptability to various imaging applications.

In summary, the document outlines the development of the 3DANN and the CLIC as innovative solutions for real-time processing of spatial-temporal problems. By leveraging hardware advancements, these technologies aim to overcome the limitations of traditional software approaches, paving the way for more efficient and effective image processing capabilities in various fields, including aerospace and beyond. The work is attributed to Tuan A. Duong and is part of NASA's ongoing efforts to push the boundaries of technology in neural network applications.