Generic structures have been conceived for multiplexer blocks to be implemented in field-programmable gate arrays (FPGAs) based on four-gate field-effect transistors (G4FETs). This concept is a contribution to the continuing development of digital logic circuits based on G4FETs and serves as a further demonstration that logic circuits based on G4FETs could be more efficient (in the sense that they could contain fewer transistors), relative to functionally equivalent logic circuits based on conventional transistors.

There are two popular categories of FPGA block structures or architectures: one based on multiplexers, the other based on lookup tables. In standard multiplexer-based architectures, the basic building block is a treelike configuration of multiplexers, with possibly a few additional logic gates such as ANDs or ORs. Interconnections are realized by means of programmable switches that may connect the input terminals of a block to output terminals of other blocks, may bridge together some of the inputs, or may connect some of the input terminals to signal sources representing constant logical levels 0 or 1.

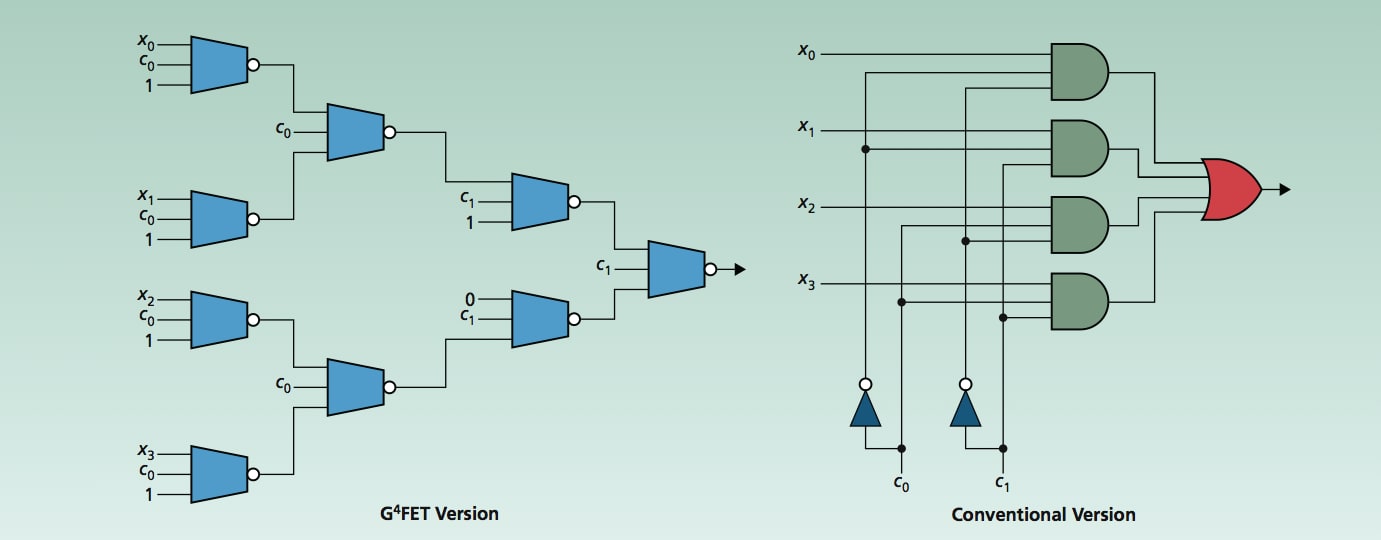

The left part of the figure depicts a four-to-one G4FET-based multiplexer tree; the right part of the figure depicts a functionally equivalent four-to-one multiplexer based on conventional transistors. The G4FET version would contains 54 transistors; the conventional version contains 70 transistors.

This work was done by Farrokh Vatan and Amir Fijany of Caltech for NASA’s Jet Propulsion Laboratory.

In accordance with Public Law 96-517, the contractor has elected to retain title to this invention. Inquiries concerning rights for its commercial use should be addressed to:

Innovative Technology Assets Management

JPL

Mail Stop 202-233

4800 Oak Grove Drive

Pasadena, CA 91109-8099

E-mail: This email address is being protected from spambots. You need JavaScript enabled to view it.

Refer to NPO-44735, volume and number of this NASA Tech Briefs issue, and the page number.

This Brief includes a Technical Support Package (TSP).

Efficient Multiplexer FPGA Block Structures Based on G4FETs

(reference NPO-44735) is currently available for download from the TSP library.

Don't have an account?

Overview

The document titled "Efficient Multiplexer FPGA Block Structures Based on G4 FETs" is a technical support package from NASA's Jet Propulsion Laboratory, focusing on advancements in field programmable gate arrays (FPGAs) utilizing G4-FET technology. It outlines the architecture and efficiency of multiplexer-based FPGA structures, emphasizing the benefits of using G4-FET devices.

FPGAs are integrated circuits that can be configured by the user after manufacturing, allowing for versatile applications in digital circuits. The document discusses two primary architectures for FPGAs: look-up table (LUT) based and multiplexer (MUX) based. The MUX-based architecture is highlighted for its efficiency in implementing logic functions through a network of multiplexers.

A key feature of the document is the introduction of a new efficient multiplexer implementation based on G4-FET devices. The G4-FET is presented as a universal and programmable logic gate that enhances the performance of multiplexer circuits. The document provides a comparative analysis of the transistor count required for different multiplexer implementations. For instance, a standard 4-to-2 multiplexer requires 70 transistors, while the G4-FET-based implementation only needs 54 transistors, showcasing a significant reduction in resource usage.

The document includes figures illustrating the architecture of a 2D-FPGA and the specific designs of 2-to-1 and 4-to-2 multiplexers using G4-FETs. These figures help visualize the efficiency and structure of the proposed designs. The G4-FET implementations are described as optimal, indicating that they are designed to achieve the best performance with the least number of components.

In summary, this technical support package provides insights into the innovative use of G4-FET technology in FPGA design, particularly in multiplexer structures. It emphasizes the advantages of reduced transistor counts and improved efficiency, making it a valuable resource for researchers and engineers in the field of digital systems and FPGA development. The document serves as a testament to NASA's commitment to advancing technology with potential applications beyond aerospace, contributing to broader technological and scientific advancements.