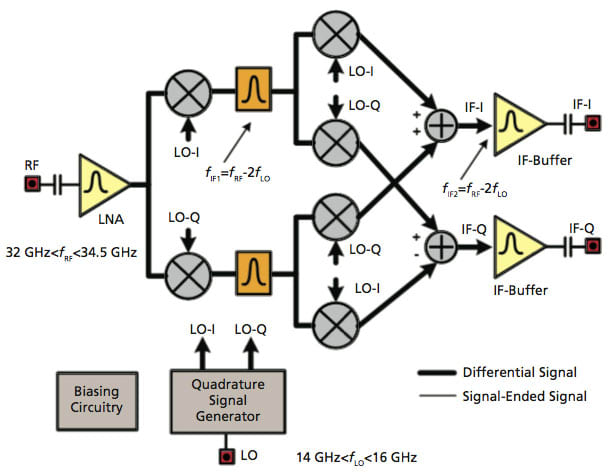

A fully integrated, front-end Ka-band monolithic microwave integrated circuit (MMIC) was developed that houses an LNA (low noise amplifier) stage, a down-conversion stage, and output buffer amplifiers. The MMIC design employs a two-step quadrature down-conversion architecture, illustrated in the figure, which results in improved quality of the down-converted IF quadrature signals. This is due to the improved sensitivity of this architecture to amplitude and phase mismatches in the quadrature down-conversion process. Current sharing results in reduced power consumption, while 3D-coupled inductors reduce the chip area. Improved noise figure is expected over previous SiGe-based, front-end designs.

This work was done by Jaikrishna Venkatesan and Narayan R. Mysoor of Caltech and Hossein Hashemi and Firooz Aflatouni of the University of Southern California for NASA’s Jet Propulsion Laboratory. For more information, download the Technical Support Package (free white paper) at www.techbriefs.com/tsp under the Electronics/Computers category. NPO-42708

This Brief includes a Technical Support Package (TSP).

Ka-Band SiGe Receiver Front-End MMIC for Transponder Applications

(reference NPO-42708) is currently available for download from the TSP library.

Don't have an account?

Overview

The document is a Technical Support Package from NASA's Jet Propulsion Laboratory (JPL) detailing the development of a Ka-Band SiGe Receiver Front-End MMIC (Monolithic Microwave Integrated Circuit) for transponder applications. It is part of NASA Tech Briefs (NPO-42708) and aims to disseminate information on aerospace-related technological advancements with potential wider applications.

The primary focus of the document is on the design and performance of a Ka-band receiver front-end that operates with a power dissipation of less than 5 mW, utilizing a SiGe process (IBM8HP). The design emphasizes the importance of power consumption, particularly highlighting that the Intermediate Frequency (IF) amplifier/buffer is the dominant factor in overall power usage. The document notes that the receiver is designed to drive a 50Ω off-chip load, which significantly influences power requirements.

Future developments are aimed at further reducing power consumption to below 1 mW and integrating additional components such as a frequency synthesizer and a complete IF chain, which includes variable gain amplifiers (VGA) and filters. This integration is expected to enhance the efficiency and functionality of the receiver.

The document also includes information about the project team, which consists of principal investigator J. Venkatesan and co-investigator N. Mysoor from JPL, along with university collaborator Hossein Hashemi and graduate student Firooz Aflatouni. The project was initiated in December 2008 as part of the Summer Undergraduate Research Program (SURP).

Additionally, the Technical Support Package provides contact information for further inquiries related to research and technology in this area, specifically through the Innovative Technology Assets Management at JPL. It emphasizes compliance with U.S. export regulations and notes that the document may contain proprietary information.

Overall, the document serves as a comprehensive overview of the Ka-Band SiGe Receiver Front-End MMIC project, outlining its objectives, design considerations, and future directions, while also promoting collaboration and innovation in aerospace technology.